深度報告 | 芯片設計EDA 2.0時代 三大路徑破解六大挑戰(zhàn)

隨著集成電路設計復雜度的指數(shù)級增長和工藝節(jié)點的持續(xù)演進,傳統(tǒng)電子設計自動化(EDA)工具與方法學正面臨前所未有的壓力。一個被稱為“EDA 2.0”的新時代已經(jīng)拉開帷幕,其核心在于通過智能化、云端化與系統(tǒng)化協(xié)同,賦能設計者應對后摩爾定律時代的嚴峻挑戰(zhàn)。本報告將深入剖析當前芯片設計面臨的六大核心挑戰(zhàn),并解讀引領產(chǎn)業(yè)變革的三大關鍵路徑。

第一部分:芯片設計面臨的六大時代挑戰(zhàn)

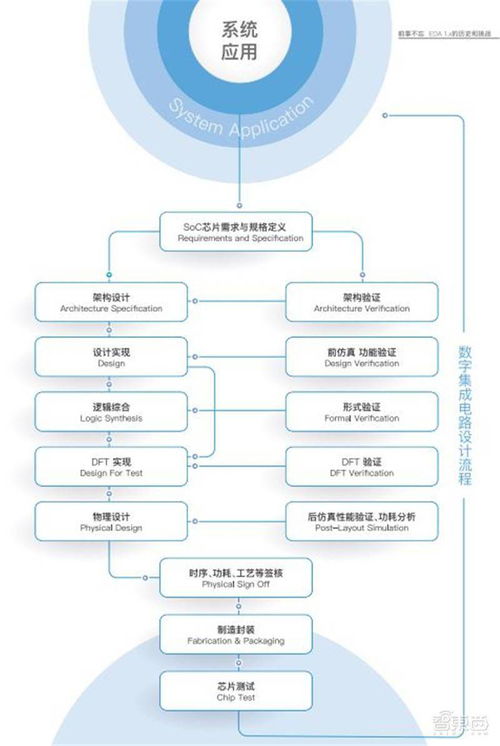

- 設計復雜度爆炸: 芯片規(guī)模已達數(shù)百億晶體管,集成IP種類繁多,軟硬件協(xié)同設計、系統(tǒng)級驗證的復雜度呈非線性攀升,傳統(tǒng)設計流程效率瓶頸凸顯。

- 物理與工藝壁壘高企: 先進工藝(如3nm及以下)帶來的物理效應(如量子隧穿、寄生效應)愈發(fā)顯著,設計與制造(DTCO)的協(xié)同需求空前強烈,對EDA工具的精度和預測能力提出極致要求。

- 研發(fā)成本與周期失控: 尖端芯片的研發(fā)投入動輒數(shù)億美元,設計、驗證、流片周期漫長,任何迭代失誤都可能導致巨大的經(jīng)濟與時間損失,市場窗口轉瞬即逝。

- 人才短缺與知識斷層: 具備尖端節(jié)點設計經(jīng)驗的專業(yè)工程師稀缺,設計方法論與工具使用門檻高,企業(yè)面臨嚴重的人才瓶頸與知識傳承困境。

- 系統(tǒng)級與多物理場優(yōu)化需求: 芯片已演變?yōu)椤跋到y(tǒng)級芯片”(SoC),需統(tǒng)籌考慮性能、功耗、面積(PPA)、信號完整性、熱管理、可靠性等多維度、多物理場的聯(lián)合優(yōu)化。

- 數(shù)據(jù)孤島與工具碎片化: 設計各階段數(shù)據(jù)格式不一,工具鏈協(xié)同不暢,數(shù)據(jù)與知識無法在流程中有效流動和復用,形成效率黑洞。

第二部分:邁向EDA 2.0的三大核心路徑

為系統(tǒng)性破解上述挑戰(zhàn),產(chǎn)業(yè)界正沿著三大路徑推動EDA向2.0階段演進:

路徑一:AI驅動的智能設計

這是EDA 2.0最顯著的標志。通過引入機器學習(ML)、深度學習(DL)等技術,將AI深度融合于設計全流程:

- 智能輔助與自動化: 在布局布線、邏輯綜合、驗證等環(huán)節(jié),AI可大幅提升效率與結果質量,如自動生成測試向量、優(yōu)化布局、預測設計熱點。

- 設計空間探索(DSE): AI能快速遍歷海量設計參數(shù)組合,尋找PPA最優(yōu)解,將傳統(tǒng)需數(shù)周的手動探索壓縮至數(shù)小時。

- 知識沉淀與復用: 學習歷史成功設計數(shù)據(jù),形成可復用的設計策略與IP,降低對個別專家經(jīng)驗的依賴,賦能普通設計團隊。

路徑二:云原生與平臺化協(xié)同

突破本地計算資源與協(xié)同模式的限制:

- 云端彈性算力: 將計算密集型的仿真、驗證、物理實現(xiàn)等任務遷移至云端,利用彈性可擴展的算力池,大幅縮短任務周期。

- 統(tǒng)一數(shù)據(jù)與平臺: 構建云原生的統(tǒng)一設計平臺,打通從架構探索、前端設計、后端實現(xiàn)到簽核的全流程數(shù)據(jù)鏈,實現(xiàn)工具無縫協(xié)同與數(shù)據(jù)的實時共享。

- 協(xié)作新模式: 支持全球分布團隊實時在線協(xié)同設計,并促進EDA廠商、設計公司、晶圓廠、IP供應商在安全可信環(huán)境下的緊密協(xié)作。

路徑三:系統(tǒng)級與多維融合設計

從“芯片設計”升維至“系統(tǒng)設計”:

- 電子系統(tǒng)級(ESL)與數(shù)字孿生: 在更高抽象層級進行系統(tǒng)架構探索與性能建模,結合數(shù)字孿生技術,實現(xiàn)軟硬件并行開發(fā)與早期驗證。

- 多物理場、多尺度仿真融合: 集成電、熱、力、電磁等多物理場分析工具,在芯片設計早期評估并優(yōu)化可靠性、散熱及信號完整性等問題。

- Chiplet與異構集成設計支持: 提供面向Chiplet(芯粒)的先進封裝協(xié)同設計、互連分析與系統(tǒng)級驗證能力,支撐異構集成這一延續(xù)摩爾定律的關鍵路徑。

與展望

EDA 2.0并非單一工具的升級,而是一場涵蓋技術、平臺與生態(tài)的范式革命。通過 “AI智能化” 提升設計自動化和決策水平,通過 “云平臺化” 重構計算模式和協(xié)作流程,通過 “系統(tǒng)融合化” 拓展設計的邊界與維度,三者交織并進,共同構成應對未來芯片設計挑戰(zhàn)的基石。

對于集成電路設計企業(yè)而言,主動擁抱EDA 2.0趨勢,重塑設計流程與方法學,將是在激烈技術競爭中獲取差異化優(yōu)勢、控制成本與風險、最終贏得市場的關鍵。EDA工具將進一步演變?yōu)榧悄芤妗f(xié)同平臺與知識載體于一體的“芯片設計大腦”,持續(xù)推動集成電路產(chǎn)業(yè)向前沿縱深突破。

如若轉載,請注明出處:http://m.lazbw.cn/product/55.html

更新時間:2026-02-20 14:57:37